什麼(me)是邏輯綜合

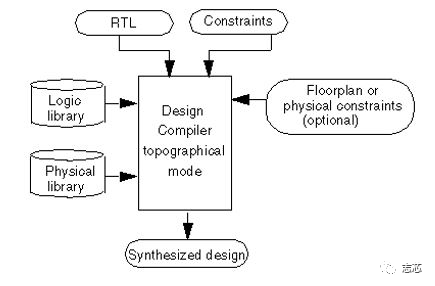

邏輯綜合是將(jiāng)較高抽象級别的設計(RTL)轉化爲可實現的較低的抽象層級的設計的過(guò)程。就(jiù)是將(jiāng)RTL轉化成(chéng)門極網表的過(guò)程。

邏輯綜合過(guò)程可以針對(duì)時(shí)序、面(miàn)積、可測性(DFT)、功耗(power)、運行時(shí)間(run time)進(jìn)行優化。

邏輯綜合的輸入文件:RTL(file list)、物理庫、時(shí)序庫、邏輯綜合flow、時(shí)序約束(clock、IO、異步設置等)、環境參數設置、upf(low power flow)。

邏輯綜合的輸出文件:netlist、sdc、ppa report等。

邏輯綜合的EDA工具:Synopsys的DC(design compiler)和Cadence的genus是廣泛使用的邏輯綜合工具。

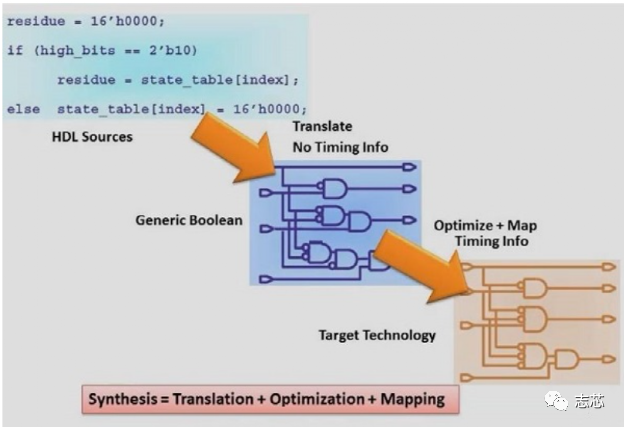

DC邏輯綜合分爲三個主要過(guò)程:翻譯(Translation)+邏輯優化(logic optimization)+門級映射(mapping)。

邏輯綜合的目标

獲得門級網表;插入時(shí)鍾門控;邏輯優化、插入DFT邏輯;保持RTL和Netlist之間的邏輯等效性。

邏輯綜合的輸入和輸出文件

輸入:RTL、library、Constraints、UPF(power intent);

輸出:Netlist、Report(Qor、Area、Timing等),UPF等

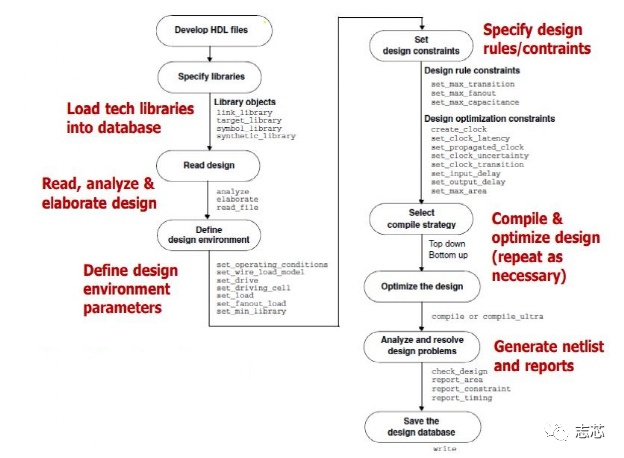

HDL文件生成(chéng)和庫

HDL文件(以VHDL或Verilog或SystemVerilog編寫);HDL分區和coding style會(huì)影響邏輯綜合和邏輯優化過(guò)程;library基于所使用的的工藝制程。

庫有不同的分類:目标庫、單元庫、符号庫、合成(chéng)庫(DesignWare)等。

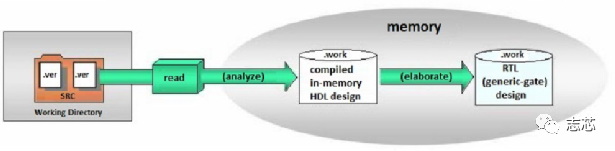

讀取文件

有兩(liǎng)種(zhǒng)方法可以將(jiāng)文件讀入DC,一種(zhǒng)是使用Analyze和Elaborate命令;另一種(zhǒng)是使用read_file命令。

Analyze命令做如下動作

讀取HDL源文件并做語法檢查和Synopsys規則檢查;

在轉化成(chéng)通用邏輯門之前,檢查文件本身的錯誤;

以中間文件的形式創建HDL庫對(duì)象;

把中間文件存儲在define_design_lib命令指定的路徑。

Elaborate做如下動作

將(jiāng)design轉化成(chéng)GTECH形式;

允許更改source file中定義的parameter;

將(jiāng)design中的算術運算符替換爲Design ware組件;

Link design;

Read file命令執行如下操作

執行與Analyze和Elaborate相同的檢查動作;

不爲verilog創建中間文件;

爲VHDL創建中間文件;

不能(néng)自動完成(chéng)link動作,需要在read_file命令完成(chéng)後(hòu),手動去做link動作;

可以讀取不同的文件格式,如VHDL、Verilog、System Verilog、ddc。

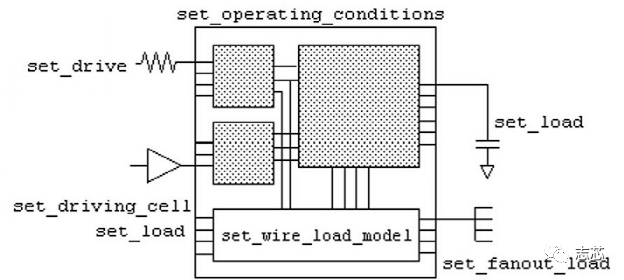

設計環境約束

讀入設計後(hòu),就(jiù)需要定義設計環境約束設計約束。Design environment包括Operating Condition 、 Wire Load Model、System interface requirements。

Operating condition:包括工藝、電壓、溫度要求(PVT);可以使用set_operating _condition在dc_setup.tcl中做相關設置。

Wire Load Model:允許DC估算net長(cháng)度和扇出對(duì)電阻、電容、net area的影響;并使用相關估算值來計算net dealy;一般,DC會(huì)使用零線負載模型。

System interface:和design交互的外部邏輯的約束,包括輸入強度設置(set_driving_cell)、輸出電容負載(set_load)、輸出扇出負載等。

可以使用report_lib、report_design等命令查看已經(jīng)加載的Design environment設置。

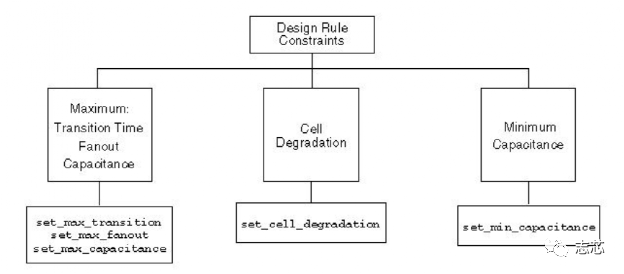

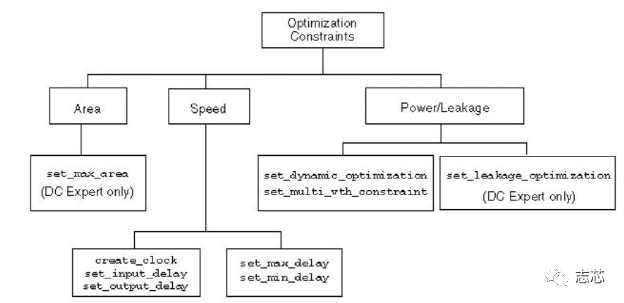

Design rule constrain和Design optimization constrain

DC進(jìn)行design優化時(shí),主要使用兩(liǎng)種(zhǒng)類型的約束。

設計規則約束(Design rule constrain):邏輯庫定義了這(zhè)種(zhǒng)隐式約束,這(zhè)些約束是design必須滿足的。默認情況下,設計規則約束優先級高于設計優化約束。

設計優化約束(Design optimization constrain):這(zhè)是顯式約束,DC會(huì)嘗試滿足這(zhè)些約束,但不會(huì)以違反設計規則約束爲代價。

DC會(huì)試圖同時(shí)滿足兩(liǎng)種(zhǒng)約束,但設計規則約束優先。

默認情況下,DC根據重要性,按以下順序考慮各種(zhǒng)約束:

設計規則約束:

Connection class、multiple port nets、maximum transition time、maximum fanout、maximum capacitance。

設計優化約束:

Maximum delay、minimum delay、maximum power、maximum area。

時(shí)序約束

時(shí)序約束需包括:時(shí)鍾、IO時(shí)序要求、組合邏輯delay要求、false path設置等。

相關鏈接:

design中的timing path之R2R

design中的timing path之I2O

design中的timing path之 R2O

Design中的timing path之 I2R

18138875980

18138875980

在線咨詢

在線咨詢