1. 拉電流和灌電流

電子元器件在廣義上分爲有源器件和無源器件。有源器件需要電源(能(néng)量)才能(néng)實現其特定的功能(néng),比如運算放大器在有輸入信号的前提下,如果不提供電源,運算放大器無法實現

其放大功能(néng)。無源器件在工作時(shí),不需要外加電源,隻要輸入信号就(jiù)能(néng)正常工作,比如在信号線上串聯33Ω的電阻,無論是否提供電源,隻要有信号經(jīng)過(guò),電阻就(jiù)能(néng)實現限流的作

用。通常定義流入器件的電流爲正,流出器件的電流爲負。

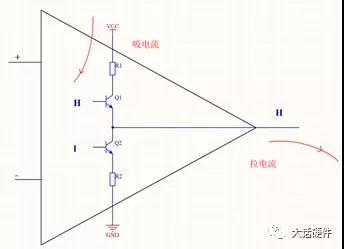

器件輸入端有電流流進(jìn)時(shí),稱爲吸電流,屬于被(bèi)動;器件輸出端有電流流出時(shí),稱爲拉電流,屬于主動;器件輸出端有電流流入時(shí),稱爲灌電流,屬于被(bèi)動。下面(miàn)以運算放大器工作

爲例。對(duì)電源來說,運算放大器屬于負載,電源提供電流讓其正常工作,此時(shí)運算放大器在吸收電流。對(duì)運算放大器來說,當它輸出高電平,提供負載電流時(shí),此時(shí)電流方向(xiàng)爲負,

稱爲拉電流;當它輸出低電平,消耗負載電流,此時(shí)電流方向(xiàng)爲正,稱爲灌電流。

2. 上/下拉電阻定義

在電子元器件間中,并不存在上拉電阻和下拉電阻這(zhè)兩(liǎng)種(zhǒng)實體的電阻,之所以這(zhè)樣(yàng)稱呼,原因是根據電阻不同使用的場景來定義的,其本質還(hái)是電阻。就(jiù)像去耦電容,耦合電容一

樣(yàng),也是根據其應用場合來取名,其本質還(hái)是電容。

上拉電阻的定義:在某信号線上,通過(guò)電阻與一個固定的高電平VCC相接,使其電壓在空閑狀态保持在VCC電平,此時(shí)電阻被(bèi)稱爲上拉電阻。

同理,下拉電阻的定義:將(jiāng)某信号線通過(guò)電阻接在固定的低電平GND上,使其空閑狀态保持GND電平,此時(shí)的電阻被(bèi)稱爲下拉電阻。

如下圖所示,R1爲上拉電阻,R2爲下拉電阻。如果R1的阻值在上百K,能(néng)提供給信号線上負載電流非常小,對(duì)負載電容充電比較慢,此時(shí)電阻被(bèi)稱爲弱上拉。

同理當下拉的電阻非常大時(shí),導緻下拉的速度比較緩慢,此時(shí)的電阻被(bèi)稱爲弱下拉。而當上下拉的電平可以提供較大的電流給芯片時(shí),此時(shí)的電阻被(bèi)稱爲是強上拉或強下拉。

3. 上/下拉電阻的應用

根據上拉電阻和下拉電阻的含義,最常見的幾種(zhǒng)用法如下。

(1)用在OC/OD門

所謂OC門就(jiù)是Open Collector,集電極開(kāi)路,所謂OD門就(jiù)是Open Drain,漏極開(kāi)路因此,OC門是針對(duì)三極管來說,OD門是針對(duì)MOS管來說。從OC門和OD電路可以看出,當輸

入電平爲H時(shí),輸出電平爲L,當輸入電平爲L時(shí),此時(shí)輸出電平爲不穩定的狀态,即高阻态,容易受到外界的幹擾。OC門和OD門不具備輸出高電平的能(néng)力。此時(shí),如果在集電極或

漏極上增加上拉電阻,當輸入爲高電平時(shí),輸出還(hái)是爲低;輸出爲低電平時(shí),輸出電平爲VCC。此時(shí)的OC門和OD門就(jiù)具備了輸出高、低電平的功能(néng),而且電平被(bèi)固定的鉗位在VCC

或者GND。

(2)用在按鍵電路

按鍵電路的工作原理是當按鍵未被(bèi)按下和按下時(shí)電平取反,MCU通過(guò)檢測到該管腳的信号電平被(bèi)取反了,判斷按鍵是否被(bèi)按下。

當按鍵未被(bèi)按下時(shí),此時(shí)MCU的IO口檢測到高電平;當按鍵被(bèi)按下時(shí),此時(shí)檢測到低電平.上拉電阻是爲了保證按鍵未被(bèi)按下時(shí)處于一個固定的高電平。

(3)用在IIC總線

IIC總線上的上拉電阻是必須要增加的,爲了保證空閑狀态時(shí),SDA和SCL都(dōu)處于高電平。

當IIC協議用在電平是3.3V以上時(shí),推薦使用4.7K的上拉電阻。當電壓小于3.3V時(shí),推薦使用2.2~3K左右的上拉電阻(經(jīng)驗值)。

(4)用在邏輯IC懸空的管腳

數字邏輯電路中由于内部邏輯門會(huì)同時(shí)開(kāi)通和關斷,SSN噪聲相比一般的電路較大,管腳懸空就(jiù)比較容易受到芯片内部和外界的電磁幹擾,在數字電路中不用的輸入腳都(dōu)要接固定電

平,通過(guò)推薦使用1k電阻接高電平或接地。

(5) 用在終端匹配

上下拉電阻經(jīng)常用在高速電路中,進(jìn)行終端匹配。由于傳輸線的阻抗不連續會(huì)引起(qǐ)信号号的反射,導緻波形出現過(guò)沖,回溝,振鈴等現象。因此,必須在傳輸上進(jìn)行源端和終端的匹

配。終端匹配常規來說具有兩(liǎng)種(zhǒng)類型,并聯端接和戴維南端接。并聯端接——在終端并聯一個與傳輸線特征阻抗一緻的電阻到VCC或者GND。終端并聯端接的優點信号能(néng)量反射回源

端之前,在負載端會(huì)消除掉,缺點是上下拉電阻會(huì)有功耗的産生。

戴維南端接——戴維南端接也稱爲分壓器端接,采用上拉電阻和下拉電阻同時(shí)接在終端上。優點是可以降低終端對(duì)源端驅動能(néng)力的要求,缺點是上下拉電阻都(dōu)存在功耗。

當然,上下拉電阻還(hái)有其他很多場合根據芯片的要求或者是電路的設計需要增加上下拉電阻。比如在電平轉換電路中,可以使用上拉電阻進(jìn)行電平之間的轉換。

在單片機驅動類似LED的負載時(shí),使用上拉電電阻可以提高I/O口的驅動能(néng)力。在三極管的BE之間增加下拉電阻,可以保證三極管在初試狀态下處于穩定關斷的狀态。

4. 上/下拉電阻的選型

(1) 從功耗消耗的角度

上拉電阻和電源相連接,下拉電阻和GND相連接,在對(duì)電阻進(jìn)行選型時(shí),需要考慮到電阻自身帶來的損耗。比如在按鍵電路中,電阻取10K可以滿足條件,取20K也可以滿足條件。

但是明顯電阻取20k時(shí),電阻消耗的能(néng)量會(huì)更低。在對(duì)待機有需求的電路中,需要嚴格控制上下拉電阻的取值。

(2) 從驅動能(néng)力的角度

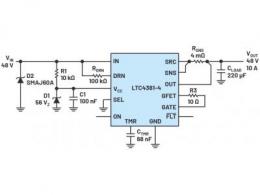

驅動能(néng)力的大小和提供的電流有關系。比如在OC門和OD門電路中,上拉電阻取太大,在輸出高電平時(shí),無法爲後(hòu)級提供較大的電流。如下圖所示,LED正常工作時(shí)需要5~10mA電

流,如果電阻取太大,LED燈無法點亮,因此需結合LED燈的電流和電壓來選取上拉電阻。

(3) 從信号速率的角度

在IIC的總線上需要增加上拉電阻,上拉電阻太大,會(huì)減慢信号由低向(xiàng)高電平轉變的時(shí)間,上升沿變緩,影響信号上速率。

根據信号上拉電阻Rp的計算公式:

其中:

Tr——信号上升沿爬升時(shí)間;

Cs——信号線上負載的寄生電容

N——信号線上并聯器件的個數;

一般在數據手冊中會(huì)提供Tr和Cs,N爲總線上并聯的器件個數和具體的使用場景有關,根據上面(miàn)的參數,可以計算出上拉電阻的值。

5. 總結

本篇文章主要從四個方面(miàn)對(duì)上下拉電阻進(jìn)行的歸納和總結。拉電流和灌電流是兩(liǎng)個經(jīng)常容易混淆的概念,因此在文章開(kāi)始就(jiù)進(jìn)行了說明。對(duì)于上下拉電阻的應用并不僅僅體現在文章中提到的5點。而在選型的時(shí)候,需要從多個角度考慮器件是否能(néng)滿足電路的需求。

18138875980

18138875980

在線咨詢

在線咨詢